# CrispyHDL

Java Inner DSL for Verilog

Nuno Paulino CTM INES C TEC

## CrispyHDL

- Binary Translation Framework required Verilog as an output target...

- How to generate Verilog systematically?

- To avoid direct string manipulation (brittle...), we employed compiler techniques (robust)

- A (nearly) complete Verilog AST package

- Verilog AST package grew → Separate CrispyHDL project

#### CrispyHDL

- Internal Java DSL for Verilog (Inspired by SpinalHDL, Chisel3, etc)

- Generation of hardware via reusable blocks exploiting high level abstractions

- Inheritance

- Generics/Templates

- Instantiation loops

- Interfaces

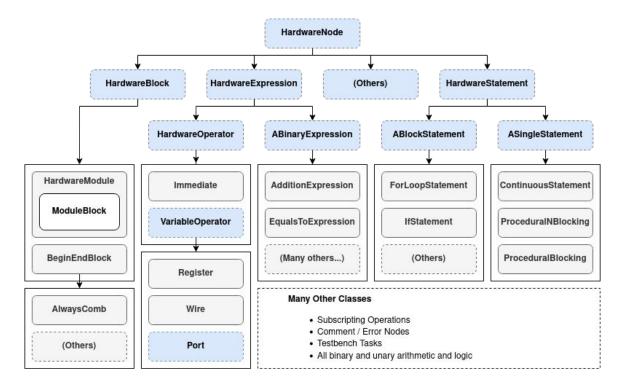

## Verilog Abstract Syntax Tree (AST) - Java Classes

- Each node

- Is a Verilog element

- Emits its respectiveVerilog source

- Trees of nodes are constructed via Java DSL to generate complete Verilog modules

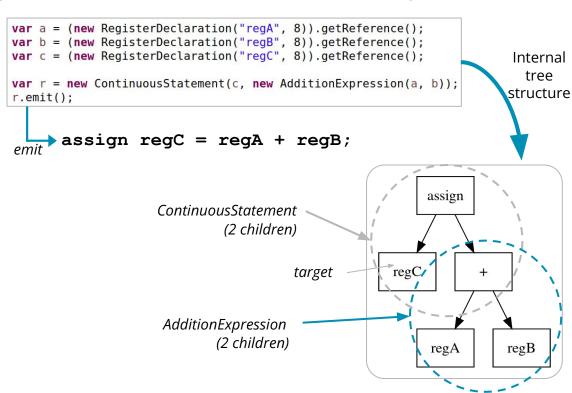

#### Verilog Abstract Syntax Tree (AST) - Example

- Simple statement example

- Crispy classes are

not meant to be

explicitly instantiated

like this

- The DSL (wrappers) hides this verbosity

## (Some) Crispy API Syntax

```

@Test

public void workshopExample4() {

// create a class which inherits the

// syntax (wrapper methods)

var ex = new HardwareModule("example");

// creates a "WireDeclaration", but returns

// a "Wire", which is a reference to the

// declared name (same for Registers and Ports)

var wire = ex.addWire("ex1", 8);

// new port

var a = ex.addInputPort("pA", 8);

// create an assign at the level of the module body

ex.assign(a, wire.lsl(2));

emit to stdout (eventually, to files)

ex.emit();

```

- There is also syntax for

- o ij

- if-else

- always ff

- always comb

- initial

- o etc...

- Some (early) handling of

- Sanity checks

- Automatic wire generation

```

module example(pA);

// Declarations block: Ports

input wire [7 : 0] pA;

// Declarations block: Wires

wire [7 : 0] ex1;

assign pA = ex1 << 8'd2;

endmodule //example</pre>

```

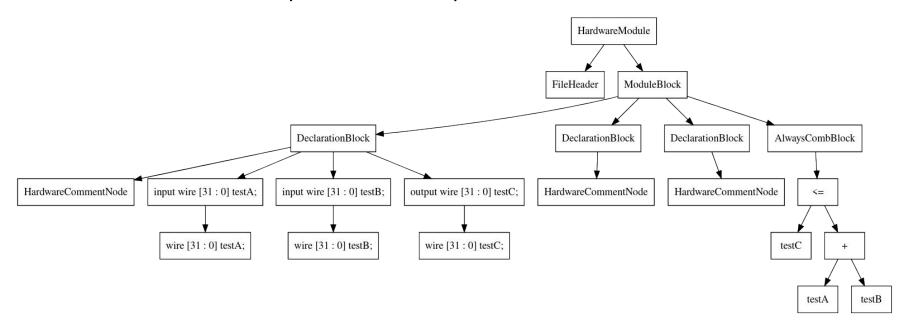

#### Programmatic Module Generation

```

module testAdder(testA, testB, testC);

public void workshopExample2() {

// Declarations block: Ports

var adder = new HardwareModule("testAdder");

input wire [31 : 0] testA;

var a = adder.addInputPort("testA", 32);

input wire [31 : 0] testB;

var b = adder.addInputPort("testB", 32);

var c = adder.addOutputPort("testC", 32);

output wire [31 : 0] testC;

adder.alwayscomb(). do(c.nonBlocking(a.add(b)));

always comb begin : comb 0

adder.emit();

testC <= testA + testB;</pre>

end

endmodule //testAdder

```

- Declaring a generic module, and then adding blocks, instances, and statements to it

- Allows for **arbitrary** module generation integrated into other flows

- But not clear if this capability is good or bad, in terms of language use/design...

- Any "HardwareModule" is never finalized (i.e., made immutable) → unless the class is made abstract (?)

#### Programmatic Module Generation

The tree structure of the previous example

#### Explicit Module Generation via Extension

```

Inherits all sugar and sanity checking methods

public class Mux2to1 extends HardwareModule

(i.e., "defines" the syntax within this class

public InputPort i0;

Public members allow easier

public InputPort i1:

public InputPort sel;

syntactic access to ports

public OutputPort out;

public Mux2to1(int bitwidth) {

super(Mux2to1.class.getSimpleName());

Some repetition is required when

i0 = addInputPort("i0", bitwidth);

i1 = addInputPort("i1", bitwidth);

ports depend on constructor

sel = addInputPort("sel", 1);

arguments... how to avoid?

out = addOutputPort("out", bitwidth);

alwayscomb("muxBlock"). ifelse(sel.not())

.then(). do(out.nonBlocking(i0))

.orElse(). do(out.nonBlocking(i1));

```

This makes Crispy more similar to Chisel or SpinalHDL, but is it the best way?

#### Module Instantiation

Still needs a significant amount of work!

#### Difficult to:

- Keep track of instances

- Define the proper abstractions

```

public class Add extends HardwareModule

public InputPort inA = addInputPort("inA", 8);

module Add3(inA, inB, inC, outD);

public InputPort inB = addInputPort("inB", 8);

public OutputPort outC = addOutputPort("outC", 8);

// Declarations block: Ports

input wire [7 : 0] inA;

public Add() {

input wire [7:0] inB;

super(Add.class.getSimpleName());

input wire [7:0] inC;

this. do(outC.nonBlocking(inA.add(inB)));

output wire [7 : 0] outD;

// Declarations block: Wires

wire [7:0] aux1;

Add Add 1926 (

.inA(inA),

public class Add3 extends HardwareModule {

.inB(inB),

.outC(aux1)

public InputPort inA = addInputPort("inA", 8);

public InputPort inB = addInputPort("inB", 8);

public InputPort inC = addInputPort("inC", 8);

public OutputPort outD = addOutputPort("outD", 8);

Add Add 1555 (

.inA(aux1),

public Add3() {

.inB(inC),

super(Add3.class.getSimpleName());

.outC(outD)

var aux1 = addWire("aux1", 8):

instantiate(new Add(), inA, inB, aux1);

endmodule //Add3

instantiate(new Add(), aux1, inC, outD):

```

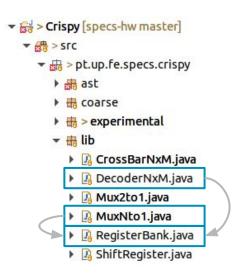

#### Future library of building blocks (?)

- Writing a register bank of arbitrary bit-width and size

- +/- 5 minutes

- Validated manually in Vivado simulation

- Future library blocks

- AXI interfaces?

- Buses?

- Caches?

- Floating point units?

#### **Current Application**

- Master's Thesis

- Generating Hardware Modules via Binary Translation of RISC-V Binaries

- Translation of RISC-V instruction sequences into Verilog (via BTF + CrispyHDL)

```

public enum RiscvPseudocode implements InstructionPseudocode {

add("RD = RA + RB;"),

sub("RD = RA - RB;"),

slt("if(signed(RA) < signed(RB)) RD = 1; else RD = 0;"),

sltu("if(unsigned(RA) < unsigned(RB)) RD = 1; else RD = 0;"),

etc...</pre>

Programmatically

Generated Modules

```

- Reimplementing the Loop Accelerator (from IEEE TLVSI 2019 paper)

- Easier/faster generation of architecture parameters

- Integrated with loop extraction and modulo-scheduling

- $\circ$  Future (partially implemented) integration with synthesis tools, reports, etc

- e.g. via generation of TCL scripts for Vivado

#### **Future Direction**

- Better abstraction and syntax

- Variable names via reflection?

- Better state keeping for module instantiation?

- Base for CGRA Architecture Exploration

- Design space exploration of CGRA variations

- Joint software / hardware compilation

- External DSL

- Tentative name: CrunchyDSL

- A dedicated parser for Crunchy to translate to internal Crispy nodes

- Avoids limitations of having Crispy implemented over Java

- Allows for context specific rules for the language